# Innovations in Glass-Based Solutions for Advanced Semicon Packaging & Consumer Electronics

**Rustom Desai**

Commercial Director, Corning Precision Glass Solutions

September 19, 2019

### **Presentation Outline**

- Why glass in semicon packaging & CE?

- Enabling glass adoption

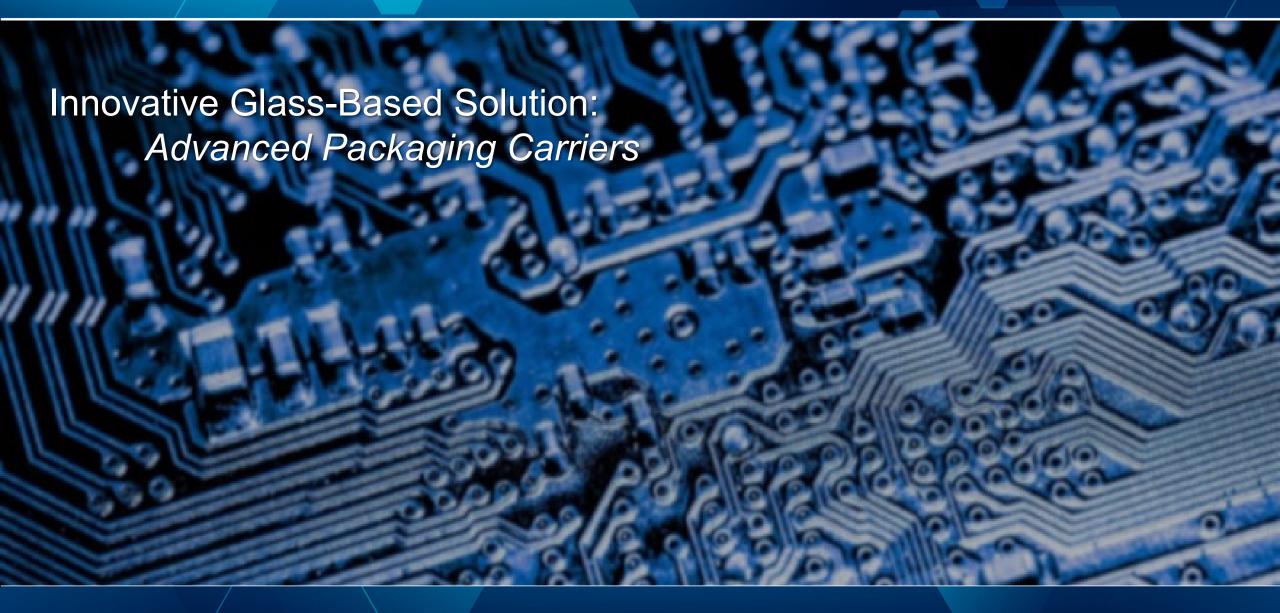

- Innovations in glass-based solutions:

- Advanced Packaging Carriers

- Wafer-Level Optics

- Augmented Reality

# Key megatrends are driving the need for glass in semiconductor processes

1. More functional, compact chips

Advanced packaging

2. Highly accurate, miniaturized sensors

Wafer-level optics

3. Faster, seamless connections

Low-loss & high linearity RF components

4. Engaging, immersive interfaces

Waveguide displays for augmented reality

Glass-based solutions enable all of these applications

# Glass is an ideal enabling material for these applications

# 1. Advanced Packaging

- ✓ Multiple CTEs & high stiffness

- ✓ Transparent

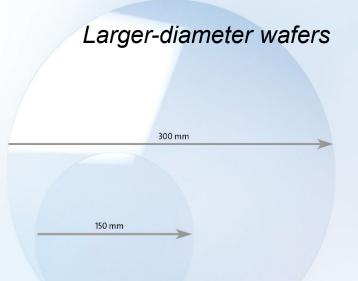

- √ Scalable

#### 2. Wafer-Level Optics

- ✓ High purity

- ✓ Multiple CTEs, refractive indices, & thicknesses

- ✓ Ultra-low TTV and warp

# 3. Low-loss, high linearity RF

- ✓ Low dielectric loss across wide frequency spectrum

- ✓ CTE match to Si possible

# 4. Waveguide-based augmented reality

- ✓ Multiple refractive indices

- ✓ Precision surface

## **Presentation Outline**

- Why glass in semicon packaging & CE?

- Enabling glass adoption

- Innovations in glass-based solutions:

- Advanced Packaging Carriers

- Wafer-Level Optics

- Augmented Reality

## **Customer Requirement #1**

# Deep technical engagement that's tailored to every development stage

#### Customer's Product Development Stages

Phase 1

Optimize

product use

Create & refine hypothesis; Manage assumptions Phase 2

Develop

& Pilot

Develop, pilot, & lock solution

Phase 3

Scale Up

"Scale solution; Grow advantage"

#### Supporting Services & Insight

Delivers shorter learning cycles, higher yields, improved product reliability

# Customer Requirement #2

# Customized material science expertise applied to specific applications

Application Examples:

Fan-Out Wafer-Level Packaging

Wafer-Level Optics & Silicon on Glass

Waveguide Eyepieces for Augmented Reality

Customer Requirements:

Minimize in-process warp

Use glass in front-end processes

Maximize field of view and visual experience

Solutions:

Advanced Packaging Carriers with high Young's Modulus and fine granularity CTEs HPFS®, an industry-leading fused silica that's 100% Si02

High refractive index glass wafers with ultra-low TTV

## **Presentation Outline**

- Why glass in semicon packaging & CE?

- Enabling glass adoption

- Innovations in glass-based solutions:

- Advanced Packaging Carriers

- Wafer-Level Optics

- Augmented Reality

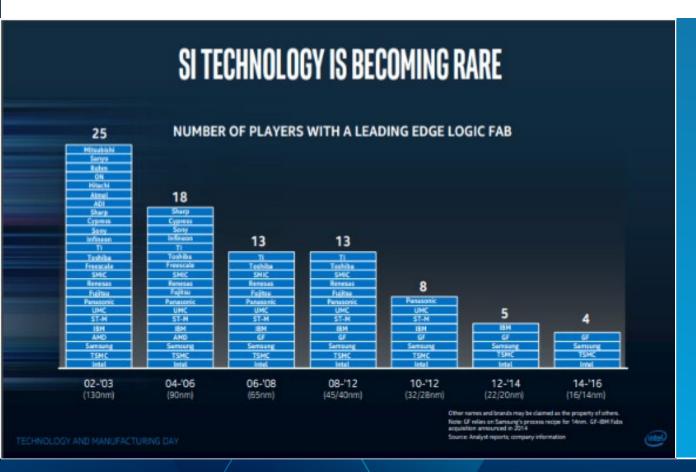

# Advanced packaging needed to deliver pace of performance improvement

- The number of foundries investing in subsequent nodes is reducing

- Time between nodes is increasing

- Many believe that advanced packaging is needed to deliver pace of performance improvements

- Example: Fan-out Packaging (FO)

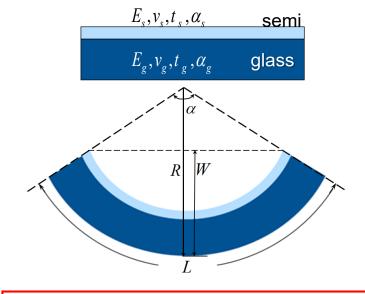

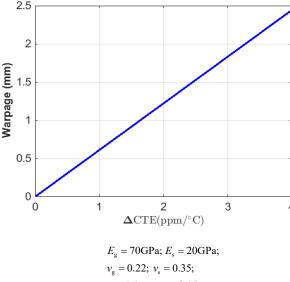

# CTE mismatch causes in-process warp

Under typical fan-out conditions, in-process warp follows a simplified formula showing its dependence on:

- 1. CTE mismatch between glass & the composite semi material

- 2. Inverse of glass Young's modulus

- 3. Inverse of square of glass thickness

$$\approx 0.75L^2\Delta\alpha\Delta T \frac{E_s(1-v_g)}{E_g(1-v_s)} \frac{t_s}{t_g^2}$$

*E*: Young's modulus; *v*: Poisson's ratio; *t*: Glass thickness;

$\alpha$ : Coefficient of thermal expansion; T: Temperature.

g: glass; s: semiconductor layers (MC + redistribution layers + die)

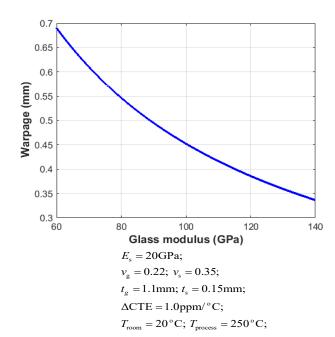

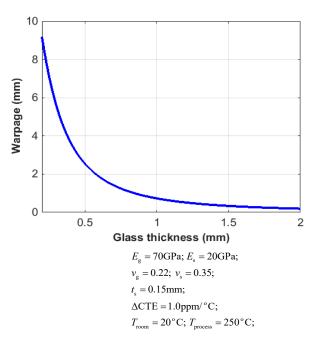

# Three glass-based levers to minimize in-process warp

#### 1. Decrease △ CTE

$t_{o} = 1.1$ mm;  $t_{s} = 0.15$ mm;

$T_{\text{room}} = 20^{\circ}\text{C}; T_{\text{process}} = 250^{\circ}\text{C};$

Challenge: Package CTE changes throughout processing

#### 2. Increase modulus

#### 3. Increase thickness

Challenge: Diminishing returns beyond 1 mm

**Advanced Packaging Carriers**

#### **Corning Advanced Packaging Carriers?**

1. Fine granularity of CTE's-minimize  $\Delta$  CTE

2. High Stiffness: Increased YM & optimized thickness

3. 4-6 week lead time for samples

# Market reaction to Corning Advanced Packaging Carriers (APC)

Currently being used in 20 customer projects

Customer: APC reduced in-process warp by **150** µm

Awarded 3D Incites 2019 Material Supplier of the Year for APC

Featured in July/Aug. issue of Chip Scale Review

# Optical sensors need to get smaller and more accurate. Enter, wafer-based *semicon processes...*

Miniaturization is driving changes in manufacturing of these sensors Front-end Back-end processes processes (FEOL) (BEOL) Each with a set of challenges Package stacking Contamination tolerance Delamination Warp

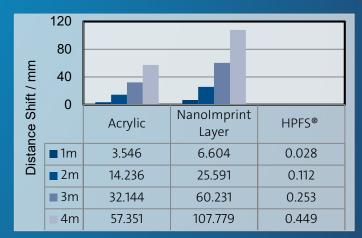

## Fused silica is FEOL-compatible

#### Corning HPFS® Fused Silica:

- ✓ Ultra-pure material: 100% SiO2

- ✓ Extreme thermal durability: Near-zero CTE

- ✓ Track record of success: HPFS has enabled 300M+ devices to date

Why HPFS is ideal for 3D sensing

High thermal durability!

# BEOL applications require a wide range of optical glasses

#### **Top Challenges**

- Package stacking tolerance

- Delamination

#### **How Glass Addresses**

✓ Tight glass geometric tolerances deliver lower stacking variance

Corning optical glasses have:

- √ 1.8x lower avg. thickness variation

- √ 1.5x lower average TTV

- √ 2.7x lower warp

- ✓ Customizing glass CTE can lower delamination stress by up to 50%, driving enhanced device reliability

- ✓ Corning provides modeling to pick optimal CTE from its portfolio

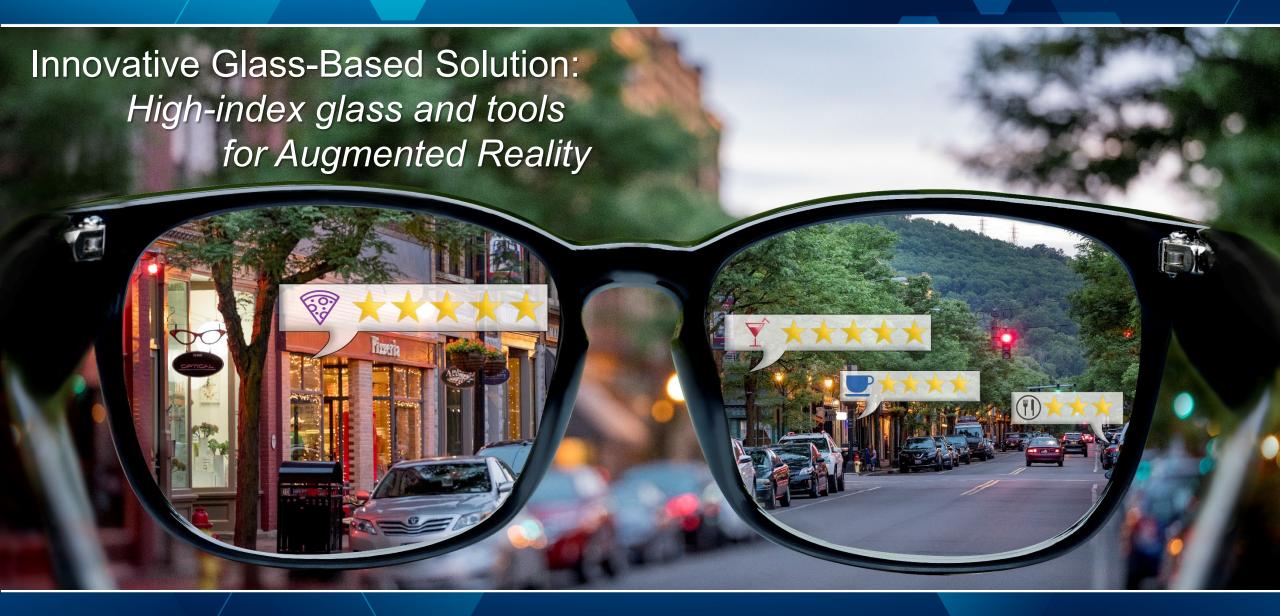

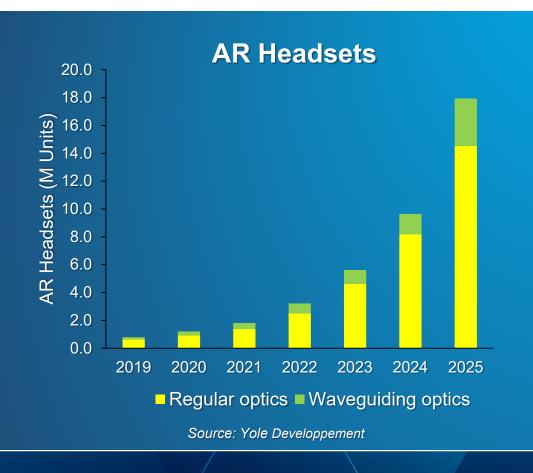

# AR headset demand is coming; *Glass with semicon-like processing* will enable engaging experiences with these devices

Waveguides require ultra-flat, high refractive index glass with gratings for a wide field of view

# Corning is enabling the emerging AR/MR supply chain

**Customer Challenges**

Wider field of view & lighter device

Higher equipment & material utilization

Higher throughput

Corning Solutions

High refractive-index glass & thinner form factors

CORNING

Reduced BoM cost

# Thank you! To learn more, visit us at booth L0916 or visit our website here: